cache du processeur

Saviez-vous ...

Cette s??lection de wikipedia a ??t?? choisi par des b??n??voles aidant les enfants SOS de Wikipedia pour cette s??lection Wikipedia pour les ??coles. parrainage SOS enfant est cool!

Un cache de processeur est un cache utilis?? par l' unit?? centrale de traitement d'un ordinateur afin de r??duire le temps moyen d'acc??s m??moire. Le cache est plus petit, plus rapide m??moire qui stocke une copie des donn??es depuis le plus fr??quemment utilis?? emplacements de m??moire principale. Aussi longtemps que la plupart des acc??s ?? la m??moire sont mises en cache emplacements de m??moire, le moyen latence d'acc??s ?? la m??moire sera plus proche de la latence de la m??moire cache de la latence de la m??moire principale.

Vue d'ensemble

Lorsque le processeur a besoin de lire ou d'??crire dans un emplacement dans la m??moire principale, il v??rifie d'abord si une copie de donn??es qui se trouve dans la m??moire cache. Dans l'affirmative, le processeur lit imm??diatement ou ??crit dans la m??moire cache, ce qui est beaucoup plus rapide que la lecture ou l'??criture vers la m??moire principale.

La plupart des CPU de bureau et serveurs modernes ont au moins trois caches ind??pendants: un cache d'instruction pour acc??l??rer instruction ex??cutable chercher, un cache de donn??es pour acc??l??rer d'extraction de donn??es et de magasin, et un Tampon de traduction (TLB) utilis?? pour acc??l??rer la traduction d'adresse virtuelle ?? physique pour les instructions et les donn??es ex??cutables. Le cache de donn??es est g??n??ralement organis?? comme une hi??rarchie de plusieurs niveaux de cache (L1, L2, etc .; voir caches multi-niveaux ).

entr??es de cache

Les donn??es sont transf??r??es entre la m??moire et le cache en blocs de taille fixe, appel??s lignes de cache. Quand une ligne de cache est copi?? de la m??moire dans la m??moire cache, une entr??e de cache est cr????. L'entr??e de cache comprendra les donn??es copi??es ainsi que l'emplacement de m??moire requise (maintenant appel?? tag).

Lorsque le processeur a besoin pour lire ou ??crire un emplacement dans la m??moire principale, il v??rifie d'abord pour une entr??e correspondante dans le cache. Les contr??les de cache pour le contenu de l'emplacement de m??moire demand??e dans toutes les lignes de cache pouvant contenir cette adresse. Si le processeur constate que l'emplacement de m??moire se trouve dans la m??moire cache, une op??ration r??ussie d'ant??m??moire se est produite (le cas contraire, un d??faut de cache). Dans le cas de:

- une op??ration r??ussie d'ant??m??moire, le processeur lit imm??diatement ou ??crit les donn??es dans la ligne de cache.

- un d??faut de cache, le cache alloue une nouvelle entr??e, et des copies des donn??es de la m??moire principale. Puis, la demande est remplie ?? partir du contenu de la m??moire cache.

les performances du cache

La proportion d'acc??s qui donnent lieu ?? une op??ration r??ussie d'ant??m??moire est appel?? le taux de succ??s, et peut ??tre une mesure de l'efficacit?? de la m??moire cache d'un programme ou algorithme donn??.

Lire la rate retarder l'ex??cution parce qu'ils n??cessitent des donn??es ?? transf??rer de la m??moire beaucoup plus lent que le cache proprement dit. Ecrire accidents peuvent se produire sans une telle peine, puisque le processeur peut continuer l'ex??cution tandis que les donn??es sont copi??es dans la m??moire principale en arri??re-plan.

caches d'instructions sont similaires ?? des caches de donn??es, mais le processeur ne effectue acc??s lire (instruction r??cup??re) dans le cache d'instruction. (Avec L'architecture de Harvard et processeurs d'architecture Harvard modifi??s, instructions et de donn??es caches peuvent ??tre s??par??s pour de meilleures performances, mais ils peuvent aussi ??tre combin??s pour r??duire la surcharge de mat??riel.)

politiques de rechange

Afin de faire de la place pour la nouvelle entr??e sur un d??faut de cache, le cache peut avoir pour expulser une des entr??es existantes. L'heuristique qu'il utilise pour choisir l'entr??e d'expulser se appelle la politique de remplacement. Le probl??me fondamental de toute politique de remplacement, ce est qu'il doit pr??dire quels entr??e de cache existante est moins susceptible d'??tre utilis?? ?? l'avenir. Pr??dire l'avenir est difficile, donc il n'y a pas de moyen parfait de choisir parmi la vari??t?? des politiques de remplacement disponibles.

Une politique de remplacement populaire, moins r??cemment utilis?? (LRU), remplace l'entr??e la moins r??cemment consult??e.

Marquage de la m??moire varie comme non-cacheable peut am??liorer les performances, en ??vitant la mise en cache des r??gions de m??moire qui sont rarement nouveau accessibles. Cela ??vite la surcharge de charger quelque chose dans le cache, sans avoir aucune r??utilisation.

- entr??es de cache peuvent ??galement ??tre d??sactiv?? ou verrouill?? en fonction du contexte.

Ecrire politiques

Si les donn??es sont ??crites dans le cache, ?? un certain moment, il doit ??galement ??tre ??crit ?? la m??moire principale. Le calendrier de cette ??criture est connu comme la politique d'??criture.

- Dans un write-through cache, chaque ??criture dans le cache provoque une ??criture ?? la m??moire principale.

- En variante, dans un reprise ou une copie-back cache, les ??critures ne sont pas imm??diatement en miroir ?? la m??moire principale. Au lieu de cela, le cache pistes quels endroits ont ??t?? ??crits sur (ces endroits sont marqu??s sale). Les donn??es de ces emplacements sont r????crites dans la m??moire principale que lorsque que les donn??es sont expuls??s de la m??moire cache. Pour cette raison, une miss de lecture dans un cache en ??criture peut parfois n??cessiter deux acc??s m??moire au service: l'un pour d'abord ??crire l'emplacement sale ?? la m??moire et puis un autre de lire le nouvel emplacement de la m??moire.

Il existe des politiques interm??diaires ainsi. Le cache peut ??tre ??criture ?? travers, mais les ??critures peut ??tre tenue ?? une file d'attente de donn??es du magasin temporairement, habituellement de sorte que plusieurs magasins peuvent ??tre trait??es ensemble (ce qui peut r??duire arr??ts de bus et d'am??liorer l'utilisation de bus).

Les donn??es en m??moire principale ??tant en cache peuvent ??tre modifi??s par d'autres entit??s (par exemple en utilisant des p??riph??riques acc??s direct ?? la m??moire ou processeur multi-core), auquel cas la copie dans le cache peuvent devenir hors de date ou vici??. Sinon, lorsque le CPU dans un processeur multi-core ?? jour les donn??es dans le cache, des copies des donn??es dans les caches associ??s avec d'autres noyaux deviendront p??rim??es. Les protocoles de communication entre les gestionnaires de cache qui maintiennent les donn??es coh??rentes sont connus comme protocoles de coh??rence de cache.

stands de CPU

Le temps n??cessaire pour aller chercher une ligne de cache de la m??moire (latence de lecture) questions parce que le CPU sera ?? court de choses ?? faire en attendant que la ligne de cache. Quand un processeur atteint cet ??tat, il est appel?? un d??crochage.

Comme les processeurs deviennent plus rapides, des stands en raison de cache miss d??placent calcul plus de potentiel; processeurs modernes peuvent ex??cuter des centaines d'instructions dans le temps pris pour aller chercher une ligne de cache unique de la m??moire principale. Diverses techniques ont ??t?? utilis??es pour maintenir le CPU occup??e pendant ce temps.

- Out-of-order processeurs (Pentium designs Intel Pro et, plus tard, par exemple) tentative d'ex??cution d'instructions ind??pendantes apr??s l'instruction qui est en attente pour les donn??es cache miss.

- Une autre technologie, utilis??e par de nombreux processeurs, est multithreading simultan?? (SMT), ou - dans la terminologie de Intel - Hyper-Threading (HT), qui permet un autre fil pour utiliser le noyau du CPU alors qu'un premier thread attend que les donn??es proviennent de la m??moire principale.

la structure d'entr??e de cache

des entr??es de lignes de cache ont g??n??ralement la structure suivante:

| balise | bloc de donn??es | bits indicateurs |

Le bloc de donn??es (ligne de cache) contient les donn??es r??elles extraites de la m??moire principale. La balise contient (une partie de) l'adresse des donn??es r??elles extraites de la m??moire principale. Les bits indicateurs sont discut??s ci-dessous.

La ??taille?? de la cache est la quantit?? de donn??es de m??moire principale qu'il peut contenir. Cette taille peut ??tre calcul??e comme le nombre d'octets stock??s dans chacun des temps de bloc de donn??es le nombre de blocs m??moris??s dans la m??moire cache. (Le nombre de marques et de drapeau de bits est pas pertinente pour ce calcul, m??me si elle ne affecte pas l'espace physique d'un cache).

Une adresse de m??moire effective est divis?? ( MSB ?? LSB) dans la balise, l'index et le d??calage de bloc.

| balise | index | le d??calage de bloc |

L'indice indique la ligne de cache (quelle ligne de cache) que les donn??es ont ??t?? mis en. La longueur d'index est  bits. Le bloc offset sp??cifie les donn??es souhait??es dans le bloc de donn??es stock?? dans la ligne de cache. Typiquement l'adresse effective est en octets, de sorte que le d??calage de longueur de bloc est

bits. Le bloc offset sp??cifie les donn??es souhait??es dans le bloc de donn??es stock?? dans la ligne de cache. Typiquement l'adresse effective est en octets, de sorte que le d??calage de longueur de bloc est  bits. L'??tiquette contient les bits les plus significatifs de l'adresse, qui sont v??rifi??es par rapport ?? la ligne courante (la ligne a ??t?? r??cup??r?? par index) pour voir si elle est celle que nous devons ou un autre emplacement, de m??moire indiff??rent que arriv?? ?? avoir les m??mes bits d'index que celle que nous voulons. La longueur d'??tiquette en bits est

bits. L'??tiquette contient les bits les plus significatifs de l'adresse, qui sont v??rifi??es par rapport ?? la ligne courante (la ligne a ??t?? r??cup??r?? par index) pour voir si elle est celle que nous devons ou un autre emplacement, de m??moire indiff??rent que arriv?? ?? avoir les m??mes bits d'index que celle que nous voulons. La longueur d'??tiquette en bits est  .

.

Certains auteurs se r??f??rent au bloc offset simplement le ??d??calage?? ou le ??d??placement??.

Exemple

Le Pentium 4 d'origine avait un ensemble cache de donn??es ?? 4 voies associative L1 de la taille de 8 Ko de cache avec des blocs de 64 octets. Par cons??quent, il ya 8 Ko / 64 = 128 blocs de cache. Si ce est associative ?? quatre voies, ce qui implique 128/4 = 32 ensembles (et donc 2 ^ 5 = 32 diff??rents indices). Il ya 64 = 2 ^ 6 d??calages possibles. Depuis l'adresse du processeur est de 32 bits, ce qui implique 32 = 21 + 5 + 6, et donc 21 bits de champ d'??tiquette. Le Pentium 4 d'origine a ??galement eu un 8-way associative cache L2 int??gr??e de la taille de 256 Ko avec 128 blocs de cache d'octets. Cela implique 32 = 17 + 8 + 7, et donc 17 bits de champ d'??tiquette.

bits de drapeau

Une cache d'instruction ne n??cessite qu'un seul bit de drapeau par entr??e de ligne de cache: un bit valide. Le bit de validit?? indique si oui ou non un bloc de cache a ??t?? charg??e avec des donn??es valides.

Au d??marrage, le mat??riel fixe tous les bits valides dans tous les caches ?? ??invalide??. Certains syst??mes ??galement mis un peu valide pour ??invalide?? ?? d'autres moments-comme lorsque multi-ma??tre bus snooping mat??riel dans le cache d'un processeur entend une adresse de diffusion d'un autre processeur, et se rend compte que certains blocs de donn??es dans le cache local sont d??sormais p??rim??es et devraient ??tre marqu??s invalide.

Un cache de donn??es n??cessite g??n??ralement deux bits de drapeau par cache entr??e de rang: un bit valide et aussi un peu sale. Le peu sale indique si ce bloc n'a pas chang?? depuis qu'il a ??t?? lu dans la m??moire principale - ??propre??, ou si le processeur a ??crit des donn??es ?? ce bloc (et la nouvelle valeur n'a pas encore fait tout le chemin ?? la m??moire principale) - ??sale??.

Associativit??

La politique de remplacement d??cide o?? dans le cache une copie d'une entr??e particuli??re de la m??moire principale ira. Si la politique de remplacement est libre de choisir ne importe quelle entr??e dans le cache de tenir la copie, le cache est appel?? enti??rement associative. ?? l'autre extr??me, si chaque entr??e dans la m??moire principale peut aller dans un seul endroit dans le cache, le cache est directement mapp??. Beaucoup de caches mettre en ??uvre un compromis dans lequel chaque entr??e dans la m??moire principale peut aller l'une quelconque des N endroits dans le cache, et sont d??crites comme jeu N-way associative. Par exemple, le cache de donn??es de niveau 1 dans un AMD Athlon est associative ?? deux voies, ce qui signifie que ne importe quel endroit particulier dans la m??moire principale peut ??tre mis en cache dans l'une des deux endroits dans le cache de donn??es de niveau 1.

Associativit?? est un troquer. Se il ya dix lieux o?? la politique de remplacement aurait pu mapp??s un emplacement m??moire, puis de v??rifier si ce dossier est dans le cache, dix entr??es de cache doivent ??tre recherch??s. V??rification plusieurs endroits prend plus de puissance, surface de la puce, et potentiellement le temps. D'autre part, les caches avec plus associativit?? souffrent moins de justesse (voir justesse de conflit, ci-dessous), de sorte que les d??chets de CPU moins de temps ?? lire de la m??moire principale lente. La r??gle de base est que le doublement de l'associativit??, ?? partir directement mapp?? ?? 2 voies, ou de 2 voies ?? 4 voies, a le m??me effet sur le taux de succ??s que doubler la taille du cache. Associativit?? augmente au-del?? 4 voies ont beaucoup moins d'effet sur le taux de succ??s, et sont g??n??ralement faites pour d'autres raisons (voir aliasing virtuel, ci-dessous).

Afin de pire, mais simple ?? mieux, mais complexe:

- cache directe mapp?? - Les meilleurs (plus rapide) hit fois, et ainsi le meilleur compromis pour les "grands" caches

- 2-way set cache associative

- 2-way biais??e de cache associative - Le meilleur compromis pour les caches dont les tailles sont dans la gamme 4K 8K-octets.

- 4-way set cache associative

- cache enti??rement associative - les meilleurs (les plus faibles) taux miss, et ainsi le meilleur compromis lorsque la peine de manquer est tr??s ??lev??

Cache direct mapped

Ici, chaque emplacement de la m??moire principale ne peut aller dans une entr??e dans le cache. Il n'a pas une politique de remplacement en tant que telle, car il n'y a pas de choix dont le contenu de l'entr??e de cache d'expulser. Cela signifie que si deux emplacements correspondent ?? la m??me entr??e, ils peuvent toujours frapper les uns les autres. Bien que simple, un cache ?? correspondance directe doit ??tre beaucoup plus grand qu'un associatifs pour donner des performances comparables, et est plus impr??visible.

2-way set cache associative

Si chaque emplacement dans la m??moire principale peut ??tre mis en cache dans deux emplacements dans le cache, une question logique est: lequel des deux Le syst??me le plus simple et le plus couramment utilis??, indiqu?? dans le sch??ma de droite ci-dessus, est d'utiliser le bits les moins significatifs de l'indice de l'emplacement de m??moire que l'indice de la m??moire cache, et ont deux entr??es pour chaque indice. Un des avantages de ce syst??me est que les ??tiquettes stock??es dans le cache ne ont pas ?? inclure cette partie de l'adresse de m??moire principale qui est impliqu??e par l'indice de la m??moire cache. Depuis les ??tiquettes d'ant??m??moire ont moins de bits, ils prennent moins d'espace sur la puce de microprocesseur et peut ??tre lu et compar?? plus rapide. Aussi LRU est particuli??rement simple car un seul bit doit ??tre stock?? pour chaque paire.

Ex??cution sp??culative

Un des avantages d'un cache mapp?? directe est qu'il permet simple et rapide la sp??culation. Une fois que l'adresse a ??t?? calcul??, l'indice d'un cache qui pourrait avoir une copie de cet emplacement en m??moire est connu. Cette entr??e de cache peut ??tre lu, et le processeur peut continuer ?? travailler avec ces donn??es avant de terminer la v??rification que l'??tiquette correspond effectivement ?? l'adresse demand??e.

L'id??e d'avoir le processeur utilise les donn??es mises en cache avant les termin??e tag match peut ??tre appliqu?? ?? associatifs caches ainsi. Un sous-ensemble de l'??tiquette, appel??e un soup??on, peut ??tre utilis?? pour choisir un seul de la possible cartographie des entr??es de cache ?? l'adresse demand??e. L'entr??e s??lectionn??e par le soup??on peut ensuite ??tre utilis?? en parall??le avec la v??rification de la balise compl??te. La technique de pointe fonctionne mieux quand il est utilis?? dans le contexte de traduction d'adresse, comme expliqu?? ci-dessous.

2-way biais??e de cache associative

Autres r??gimes ont ??t?? propos??s, tels que le cache asym??trique, o?? l'indice pour la voie 0 est directe, comme ci-dessus, mais l'indice de mani??re 1 est form??e avec une fonction de hachage. Une bonne fonction de hachage a la propri??t?? qui traite qui entrent en conflit avec le mappage direct tend pas ?? des conflits lors de la projection avec la fonction de hachage, et il est donc moins probable qu'un programme souffrir d'un nombre inattendu de conflit rate en raison d'un acc??s pathologique motif. L'inconv??nient est la latence suppl??mentaire de calcul de la fonction de hachage. En outre, lorsque vient le temps de charger une nouvelle ligne et d'expulser une ancienne ligne, il peut ??tre difficile de d??terminer ce qui a ??t?? ligne existante moins r??cemment utilis??, parce que les nouveaux conflits de ligne avec des donn??es ?? diff??rents indices dans chaque sens; Suivi LRU pour les caches non-biais??es se fait g??n??ralement sur une base per-mis. N??anmoins, caches asym??triques associatif ont des avantages majeurs sur les set-associative classiques.

cache pseudo-associative

Un v??ritable jeu de cache-associative teste tous les moyens possibles simultan??ment, en utilisant quelque chose comme un m??moire adressable par contenu. Un cache de pseudo-associatif teste chaque chemin possible une ?? la fois. Un cache-resuc??e hachage et un cache de colonne associatif sont des exemples de cache de pseudo-associatif.

Dans le cas fr??quent de trouver un succ??s de la premi??re mani??re test??, un cache de pseudo-associatif est aussi rapide qu'un cache en correspondance directe. Mais il a un taux de miss conflit beaucoup inf??rieur ?? un cache ?? correspondance directe, plus proche du taux d'un cache enti??rement associative miss.

Cache manquer

A d??faut de cache fait r??f??rence ?? une tentative avort??e de lire ou d'??crire un morceau de donn??es dans le cache, ce qui se traduit par un acc??s de m??moire principale avec beaucoup plus de latence. Il existe trois types de d??fauts de cache: lecture d'instruction miss, donn??es lues miss, et d'??criture de donn??es manquer.

Un cache lu Mlle d'une cache d'instruction provoque g??n??ralement le plus de retard, parce que le processeur, ou du moins la thread d'ex??cution, doit attendre (d??crochage) jusqu'?? ce que l'instruction est extraite de la m??moire principale.

Un cache de lecture manqu?? d'un cache de donn??es provoque g??n??ralement moins de retard, parce que les instructions ne d??pendant pas de la lecture de cache peuvent ??tre ??mises et continuent ex??cution jusqu'?? ce que les donn??es sont renvoy??es de la m??moire principale, et les instructions d??pendantes peut reprendre l'ex??cution.

Un cache ??criture manquer ?? un cache de donn??es provoque g??n??ralement le moindre retard, parce que l'??criture peut ??tre en file d'attente et il ya quelques limitations sur l'ex??cution des instructions ult??rieures. Le processeur peut continuer jusqu'?? ce que la file d'attente est pleine.

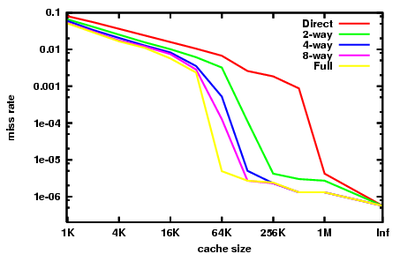

Afin de r??duire les taux de d??faut de cache, une grande partie de l'analyse a ??t?? faite sur le comportement du cache dans une tentative de trouver la meilleure combinaison de la taille, associativit??, taille de bloc, et ainsi de suite. S??quences de r??f??rences de m??moire effectu??es par des programmes de r??f??rence sont enregistr??s en tant que traces d'adresse. Des analyses ult??rieures simuler de nombreux designs possible de cache sur ces traces d'adresses longues. Donner un sens de la fa??on dont les nombreuses variables influent sur le taux d'utilisation du cache peut ??tre assez d??routant. Une contribution significative ?? cette analyse a ??t?? faite par Mark Hill, qui se est s??par?? de justesse en trois cat??gories (connu sous le nom des Trois Cs):

- Manque obligatoires sont ces accidents caus??s par la premi??re r??f??rence ?? un emplacement en m??moire. Taille du cache et l'associativit?? ne font aucune diff??rence au nombre d'??checs obligatoires. Pr??chargement peut aider ici, comme des tailles de bloc plus grande de cache (qui sont une forme de prefetching). Manque obligatoires sont parfois appel??s accidents que froides.

- manque de capacit?? sont les accidents qui se produisent ind??pendamment de l'associativit?? ou la taille de bloc, uniquement en raison de la taille limit??e de la m??moire cache. La courbe de taux de manquer de capacit?? par rapport ?? la taille du cache donne une mesure de la localisation temporelle d'un courant de r??f??rence particulier. Notez qu'il n'y a pas de notion utile d'un cache ??tant ??complet?? ou ??vide?? ou ??presque ?? pleine capacit??": caches CPU ont presque toujours ?? peu pr??s chaque ligne rempli d'une copie de quelque ligne de la m??moire principale, et presque chaque attribution d'une nouvelle ligne n??cessite l'expulsion d'une ancienne ligne.

- manque de conflit sont les accidents qui auraient pu ??tre ??vit??es, avaient le cache pas expuls??s ?? une date ant??rieure. manque de conflits peuvent ??tre subdivis??es en manque de cartographie, qui sont in??vitables ??tant donn?? une quantit?? particuli??re de l'associativit??, et manque de remplacement, qui sont dues au choix de la victime notamment de la politique de remplacement.

Le graphique de droite pr??sente le rendement de cache vu sur la partie enti??re de la benchmarks SPEC CPU2000, telles que recueillies par Hill et Cantin. Ces rep??res sont destin??s ?? repr??senter le type de charge de travail qu'un poste de travail d'ing??nierie pourrait voir un jour donn??. Le lecteur doit garder ?? l'esprit que la recherche de rep??res qui sont encore utilement repr??sentant de nombreux programmes a ??t?? tr??s difficile, et il y aura toujours d'importants programmes au comportement tr??s diff??rent de ce qui est montr?? ici.

Nous pouvons voir les diff??rents effets des trois Cs dans ce graphique.

Au extr??me droite, avec la taille de cache marqu?? "Inf", nous avons les accidents obligatoires. Si nous voulons am??liorer la performance d'une machine sur SPECint2000, en augmentant la taille du cache au-del?? de 1 Mo est essentiellement futile. Ce est l'intuition donn??e par les accidents obligatoires.

Le taux de d??faut de cache enti??rement associative ici est presque repr??sentant du taux de miss capacit??s. La diff??rence est que les donn??es pr??sent??es sont des simulations supposant une Politique de remplacement LRU. Afficher le taux capacit??s miss n??cessiterait une politique de remplacement parfait, ce est ?? dire un oracle qui ressemble ?? l'avenir de trouver une entr??e de cache qui est fait ne va pas ??tre frapp??.

Notez que notre rapprochement du taux de miss capacit?? tombe ?? pic entre 32 kB et 64 ko. Ceci indique que l'indice de r??f??rence a une jeu de travail d'environ 64 ko. Un concepteur de cache du processeur d'examiner ce point de r??f??rence aura un fort int??r??t ?? d??finir la taille du cache ?? 64 Ko plut??t que 32 Ko. Notez que, sur ce point de rep??re, aucun montant de l'associativit?? peut faire un cache 32 kB effectuer ainsi que 64 Ko ?? 4 voies, ou m??me un 128 Ko de cache ?? correspondance directe.

Enfin, notez que entre 64 Ko et 1 Mo il ya une grande diff??rence entre caches directs mapp??s et enti??rement associatives. Cette diff??rence est le taux de miss conflit. L'id??e de regarder ?? taux de manquer de conflit est que les caches secondaires b??n??ficient beaucoup de la haute associativit??.

Cet avantage ??tait bien connu dans les ann??es 80 et au d??but des ann??es 90, lorsque les concepteurs de CPU ne ont pas pu se adapter ?? de grandes caches sur puce, et n'a pas pu obtenir suffisamment de bande passante soit sur la m??moire cache de donn??es ou une ??tiquette m??moire cache pour mettre en ??uvre haute associativit?? dans des caches hors puce . Hacks Housewives ont ??t?? tent??es: le MIPS R8000 utilis?? cher hors puce tag d??di?? SRAM, qui avaient embarqu??s comparateurs de tag et de grands pilotes sur les lignes de match, afin de mettre en ??uvre un 4 Mo ?? 4 voies cache associative. Le MIPS R10000 utilis?? puces SRAM ordinaires pour les tags. acc??s Tag pour les deux fa??ons fallu deux cycles. Pour r??duire la latence, le R10000 serait deviner de quel c??t?? de la cache aurait frapp?? sur chaque acc??s.

La traduction d'adresse

La plupart des processeurs ?? usage g??n??ral de mettre en ??uvre une certaine forme de m??moire virtuelle. Pour r??sumer, chaque programme se ex??cutant sur la machine voit sa propre simplifi??e espace d'adressage, qui contient du code et des donn??es pour seulement ce programme. Chaque programme utilise cet espace d'adressage virtuel, sans ??gard pour le cas o?? elle existe dans la m??moire physique.

M??moire virtuelle n??cessite le processeur pour traduire des adresses virtuelles g??n??r??es par le programme en adresses physiques dans la m??moire principale. La partie du processeur qui ne cette traduction est connu comme le Unit?? de gestion de m??moire (MMU). Le chemin d'acc??s rapide par la MMU peut effectuer ces traductions stock??es dans la Tampon de traduction (TLB), qui est un cache de mappage ?? partir du syst??me d'exploitation de table de page.

Aux fins de la pr??sente discussion, il ya trois ??l??ments importants de traduction d'adresse:

- Latence: L'adresse physique est disponible aupr??s de la MMU un certain temps, peut-??tre quelques cycles, apr??s l'adresse virtuelle est disponible ?? partir du g??n??rateur d'adresses.

- Aliasing: adresses virtuelles multiples peuvent mapper vers une adresse physique unique. La plupart des processeurs garantissent que tous les mises ?? jour de cette adresse physique unique qui se passera dans l'ordre du programme. Pour se acquitter de cette garantie, le processeur doit se assurer qu'une seule copie d'une adresse physique se trouve dans le cache ?? un moment donn??.

- Granularit??: L'espace d'adressage virtuel est divis?? en pages. Par exemple, un 4 Go espace d'adressage virtuel peut ??tre d??coup?? en 1.048.576 pages de 4 Ko de taille, dont chacun peut ??tre mapp??s ind??pendamment. Il peut y avoir plusieurs formats de page pris en charge; voir m??moire virtuelle pour l'??laboration.

Une note historique: certains syst??mes de m??moire virtuelle d??but ??tait tr??s lent, car elles n??cessitaient un acc??s ?? la table de page (tenue ?? la m??moire principale) avant chaque acc??s programm?? ?? la m??moire principale. En l'absence de cache, cette coupe efficacement la vitesse de la machine en deux. Le premier cache mat??riel utilis?? dans un syst??me informatique ne ??tait pas en fait un cache de donn??es ou d'instructions, mais plut??t un TLB.

Les caches peuvent ??tre divis??s en quatre types, selon que l'indice ou de l'??tiquette correspondent ?? des adresses physiques ou virtuels:

- Physiquement index??, marqu??s physiquement (PIPT) caches utilisent l'adresse physique pour l'indice et l'??tiquette. Bien que ce est simple et ??vite les probl??mes avec aliasing, il est aussi lent, que l'adresse physique doit ??tre leva les yeux (ce qui pourrait impliquer une miss TLB et l'acc??s ?? la m??moire principale) avant cette adresse peut ??tre recherch??e dans le cache.

- Pratiquement index??, pratiquement marqu??s (VIVT) caches utilisent l'adresse virtuelle ?? la fois pour l'indice et l'??tiquette. Ce syst??me de mise en cache peut entra??ner des recherches beaucoup plus rapides, puisque la MMU n'a pas besoin d'??tre consult??s d'abord d??terminer l'adresse physique pour une adresse virtuelle donn??e. Cependant, VIVT souffre de probl??mes d'aliasing, o?? plusieurs adresses virtuelles diff??rentes peuvent se r??f??rer ?? la m??me adresse physique. Le r??sultat est que ces adresses seront mises en cache s??par??ment en d??pit de r??f??rence ?? la m??me m??moire, provoquant des probl??mes de coh??rence. Un autre probl??me est homonymes, o?? la m??me adresse virtuelle Cartes ?? plusieurs adresses physiques diff??rentes. Il ne est pas possible de distinguer ces mappages en ne regardant ?? l'index virtuel, si les solutions possibles comprennent: vider le cache apr??s une changement de contexte, for??ant espaces d'adressage d'??tre non-chevauchement, le marquage de l'adresse virtuelle avec un ID d'espace d'adresse (ASID), ou en utilisant des ??tiquettes physiques. En outre, il ya un probl??me que virtuel-physique mappages peuvent changer, ce qui n??cessiterait rin??age lignes de cache, comme le SAV ne serait plus valide.

- , Marqu??s physiquement (VIPT) caches Pratiquement index??s utilisent l'adresse virtuelle pour l'index et l'adresse physique dans la balise. L'avantage par rapport PIPT est une latence plus faible, comme la ligne de cache peut ??tre consid??r??e en parall??le avec la traduction TLB, mais l'??tiquette ne peut ??tre compar??e jusqu'?? l'adresse physique est disponible. L'avantage par rapport VIVT est que, depuis la balise poss??de l'adresse physique, le cache peut d??tecter homonymes. VIPT n??cessite plus de bits d'??tiquette, que les bits d'index ne repr??sentent plus la m??me adresse.

- Physiquement index??, pratiquement marqu??s (PIVT) caches ne sont que th??oriques car ils seraient pour l'essentiel inutile.

La vitesse de cette r??currence (le temps de latence de charge) est cruciale pour les performances du processeur, et ainsi plus modernes niveau 1 caches sont quasiment index??, ce qui permet au moins TLB la recherche de la MMU de proc??der en parall??le avec la r??cup??ration des donn??es du cache RAM.

Mais indexation virtuelle ne est pas le meilleur choix pour tous les niveaux de cache. Le co??t de traiter les alias virtuels cro??t avec la taille de la m??moire cache, et par cons??quent la plupart de niveau 2 et les grandes caches sont index??s physiquement.

Caches ont toujours utilis?? les deux adresses virtuelles et physiques pour les ??tiquettes d'ant??m??moire, bien marquage virtuelle est maintenant rare. Si la recherche TLB peut terminer avant la recherche de cache RAM, l'adresse physique est disponible ?? temps pour comparer tag, et il ne est pas n??cessaire pour le marquage virtuel. Grandes caches, puis, ont tendance ?? ??tre marqu??s physiquement, et seulement de petites caches de latence tr??s faibles sont pratiquement ??tiquet??s. Dans processeurs r??cents d'usage g??n??ral, le marquage virtuelle a ??t?? remplac?? par vhints, comme d??crit ci-dessous.

Homonymes et synonymes probl??mes

Le cache qui repose sur l'indexation et le marquage virtuel devient incompatible apr??s la m??me adresse virtuelle est mapp?? dans diff??rentes adresses physiques ( homonyme). Cela peut ??tre r??solu en utilisant l'adresse physique pour le marquage ou en stockant l'espace adresse id dans la ligne de cache. Cependant, le dernier de ces deux approches ne aide pas contre le probl??me de synonymes, o?? plusieurs lignes d'ant??m??moire finissent stocker des donn??es pour la m??me adresse physique. ??crit ?? tel endroit peut mettre ?? jour un seul endroit dans le cache, en laissant les autres avec des donn??es incoh??rentes. Ce probl??me pourrait ??tre r??solu par l'aide des configurations de m??moire non se chevauchent pour les diff??rents espaces d'adressage ou autrement, le cache (ou une partie de celui-ci) doit ??tre rinc??e lorsque les modifications de mappage.

Tags et vhints virtuelles

Le grand avantage de balises virtuelles est que, pour les caches associatifs, ils permettent au match d'??tiquette de proc??der avant le virtuel ?? la traduction physique est fait. Cependant,

- sondes de coh??rence et les expulsions pr??sentent une adresse physique d'action. Le mat??riel doit avoir un moyen de convertir les adresses physiques dans un index de m??moire cache, g??n??ralement en stockant balises physiques ainsi que des balises virtuelles. A titre de comparaison, un cache physiquement marqu?? n'a pas besoin que les ??tiquettes restent virtuelles, qui est plus simple.

- Quand un virtuel pour la cartographie physique est supprim?? du TLB, les entr??es de cache avec ces adresses virtuelles devront ??tre rinc?? en quelque sorte. Alternativement, si les entr??es de cache sont autoris??s sur les pages non cartographi??s par le TLB, alors ces entr??es devront ??tre rinc?? lorsque les droits d'acc??s sur ces pages sont modifi??es dans le tableau de la page.

Il est ??galement possible pour le syst??me d'exploitation pour se assurer qu'aucun alias virtuels sont simultan??ment r??sident dans la m??moire cache. Le syst??me d'exploitation fait de cette garantie par l'application de coloriage, qui est d??crit ci-dessous. Certains processeurs RISC d??but (SPARC, RS / 6000) ont cette approche. Il n'a pas ??t?? utilis?? r??cemment, que le co??t du mat??riel de d??tection et d'expulsion alias virtuels a diminu?? et la complexit?? du logiciel et de la p??nalit?? de performance parfaite coloration page a augment??.

Il peut ??tre utile de distinguer les deux fonctions de balises dans un cache associatif: ils sont utilis??s pour d??terminer quel chemin de l'entr??e fix?? pour s??lectionner, et ils sont utilis??s pour d??terminer si le cache touch?? ou manqu??. La deuxi??me fonction doit toujours ??tre correcte, mais il est permis pour la premi??re fonction ?? deviner, et d'obtenir la mauvaise r??ponse occasionnellement.

Certains processeurs (par exemple d??but SPARCS) ont caches avec les deux balises virtuels et physiques. Les balises virtuels sont utilis??s pour la s??lection de chemin, et les balises physiques sont utilis??s pour d??terminer tout ou rien. Ce type de cache b??n??ficie de l'avantage d'un temps de latence cache pratiquement balis??, et l'interface logicielle simple d'un cache physiquement marqu??. Elle porte le co??t suppl??mentaire des ??tiquettes dupliqu??es, cependant. En outre, pendant le traitement de miss, les autres moyens de la ligne de cache index??es doivent ??tre sond?? pour les alias virtuels et tout matchs expuls??es.

La zone suppl??mentaire (et une certaine latence) peuvent ??tre att??nu??s en gardant des notes virtuelles ?? chaque entr??e ?? la place de balises virtuelles de cache. Ces conseils sont un sous-ensemble ou de hachage de la balise virtuelle, et sont utilis??es pour s??lectionner le chemin de la m??moire cache ?? partir de laquelle d'obtenir des donn??es et une ??tiquette physique. Comme un cache pratiquement balis??, il peut y avoir un match de soup??on, mais tag d??calage physique virtuelle, dans ce cas, l'entr??e de cache avec l'indice correspondant doit ??tre expuls?? sorte que cache acc??de apr??s la cache remplir ?? cette adresse aura un seul match de conseil. Depuis conseils virtuels ont moins de bits que les ??tiquettes virtuelles qui les distinguent les uns des autres, un cache pratiquement laiss?? entendre souffre plus de manque de conflit que d'un cache pratiquement balis??.

Peut-??tre la r??duction d??finitive de notes virtuels peut ??tre trouv?? dans les Pentium 4 Willamette (noyaux et Northwood). Dans ces processeurs du soup??on virtuelle est effectivement 2 bits, et le cache est associative 4 voies. En effet, le mat??riel maintient une simple permutation de l'adresse virtuelle ?? l'index de la m??moire cache, de sorte qu'aucune contenu m??moire adressable (CAM) est n??cessaire pour s??lectionner le droit l'une des quatre fa??ons par les cheveux.

Coloriage

Grandes caches physiquement index??es (g??n??ralement des caches secondaires) rencontrez un probl??me: le syst??me d'exploitation plut??t que les contr??les de l'application qui se entrechoquent pages avec l'autre dans le cache. Les diff??rences dans l'allocation de pages d'un programme de fonctionner ?? l'autre conduisent ?? des diff??rences dans les habitudes cache de collision, ce qui peut conduire ?? de tr??s grandes diff??rences dans la performance du programme. Ces diff??rences peuvent rendre tr??s difficile d'obtenir un calendrier coh??rent et reproductible pour une course de r??f??rence.

Pour comprendre le probl??me, envisager un CPU avec une MB physiquement index?? niveau 2 cache direct mapped et pages de 4 Ko de m??moire virtuelle. Pages physiques s??quentielles correspondent aux emplacements s??quentiels dans le cache qu'apr??s 256 pages le mod??le se enroule autour. Nous pouvons ??tiqueter chaque page physique avec une couleur de 0-255 pour d??signer o?? dans le cache, il peut aller. Endroits ?? l'int??rieur des pages physiques avec des couleurs diff??rentes ne peuvent pas entrer en conflit dans le cache.

Un programmeur essayant de faire une utilisation maximale de la m??moire cache peut organiser les mod??les d'acc??s de son programme de sorte que seuls 1 Mo de donn??es doivent ??tre mis en cache ?? un moment donn??, ??vitant ainsi de justesse de capacit??. Mais il doit aussi se assurer que les mod??les d'acc??s ne ont pas manque de conflit. Une fa??on de penser ?? propos de ce probl??me est de diviser les pages virtuelles le programme utilise et leur attribuer des couleurs virtuelles de la m??me mani??re que les couleurs physiques ont ??t?? affect??s ?? des pages physiques avant. Le programmeur peut alors organiser les motifs de son code d'acc??s de sorte que deux pages de la m??me couleur virtuelle sont utilis??s en m??me temps. Il ya une grande litt??rature sur ces optimisations (par exemple, boucle de l'optimisation du nid), venant en grande partie de la High Performance Computing (HPC) de la communaut??.

Le hic, ce est que, bien que toutes les pages de l'utilisation ?? un moment donn?? peuvent avoir des couleurs diff??rentes virtuelles, certains peuvent avoir les m??mes couleurs physiques.En fait, si le système d'exploitation affecte pages physiques vers des pages virtuelles de façon aléatoire et uniformément, il est très probable que certaines pages auront la même couleur physique, puis les emplacements de ces pages vont entrer en collision dans le cache (ce qui est leparadoxe de l'anniversaire).

La solution est d'avoir la tentative de système d'exploitation pour affecter différentes pages de couleur physique à différentes couleurs virtuels, une technique appelée coloriage . Bien que la cartographie réelle du virtuel à la couleur physique est sans rapport avec les performances du système, applications impairs sont difficiles à suivre et peu d'avantages, donc la plupart des approches de coloriage simplement essayer de garder les couleurs physiques et virtuels de page même.

Si le système d'exploitation peut garantir que chacune des cartes physiques de pages à une seule couleur virtuelle, alors il n'y a pas alias virtuels, et le processeur peuvent utiliser des caches quasiment indexés sans avoir besoin de sondes d'alias virtuels supplémentaires lors de la manipulation de manquer. Alternativement, l'O / S peut vider une page à partir du cache chaque fois qu'il change d'une couleur virtuelle à l'autre. Comme mentionné ci-dessus, cette approche a été utilisée pour certains SPARC début et RS / 6000 dessins.

hiérarchie de cache dans un processeur moderne

Les processeurs modernes ont de multiples caches interagissant sur ??????puce.

Le fonctionnement d'un cache particulier peut être complètement spécifié par:

- la taille du cache

- la taille de bloc du cache

- le nombre de blocs dans un ensemble

- la politique de remplacement de cache définir

- la politique cache d'écriture (write-through ou reprise)

Bien que tous les blocs de cache dans un cache particulier, sont de la même taille et le même associativité, typiquement caches "de niveau inférieur" (tels que le cache L1) ont une taille plus petite, ont de plus petits blocs, et ont moins de blocs dans un ensemble , tandis que les caches "de niveau supérieur" (tels que le cache L3) ont une plus grande taille, de plus grands blocs, et plusieurs blocs dans un ensemble.

Caches spécialisés

Pipeline m??moire de CPU ?? partir de plusieurs points de la pipeline: extraction d'instruction, la traduction d'adresse virtuelle à physique, et d'extraction de données (voir pipeline classique RISC). La conception naturelle est d'utiliser différents caches physiques pour chacun de ces points, de sorte que pas une ressource physique doit être prévue pour desservir deux points dans le pipeline. Ainsi le pipeline se termine naturellement avec au moins trois caches séparés (instruction, TLB, et de données), chacune spécialisée à son rôle particulier.

Pipelines d'instructions et de données caches séparés, désormais prédominants, sont dit avoir une architecture de Harvard. À l'origine, cette phrase fait référence à des machines avec instructions et de données des mémoires séparées, qui se sont avérés ne pas du tout populaire. La plupart des processeurs modernes ont une mémoire unique architecture de von Neumann.

cache des victimes

Un cache de la victime est un cache utilisé pour contenir des blocs expulsées d'un cache du processeur lors de leur remplacement. Le cache de la victime se trouve entre la cache principale et son chemin de recharge, et ne détient que des blocs qui ont été expulsées de la cache principale. Le cache de la victime est généralement entièrement associative, et est destiné à réduire le nombre d'accidents de conflit. Beaucoup de programmes couramment utilisés ne nécessitent pas une cartographie associative pour tous les accès. En fait, seule une petite fraction de l'accès à la mémoire du programme exigent haute associativité. Le cache de la victime exploite en fournissant haute associativité à ces seuls accès de cette propriété. Il a été introduit par Norman Jouppi de DEC en 1990.

cache de Trace

Un des exemples les plus extrêmes de cache spécialisation est le cache de trace trouvés dans les processeurs Intel Pentium 4 microprocesseurs. Un cache de trace est un mécanisme pour augmenter l'instruction chercher bande passante et la consommation d'énergie (dans le cas du Pentium 4) en stockant des traces d' instructions qui ont déjà été récupérées et décodés.

La publication universitaire plus tôt largement reconnu de cache de trace était parEric Rotenberg,Steve Bennett etJim Smith dans leur rapport de 1996«Trace Cache: une latence faible approche à l'instruction de haute bande passante Comparaison."

Une publication antérieure est le brevet américain 5,381,533, «Dynamic mémoire cache d'instruction de flux organisé autour de segments de traces indépendants de la ligne d'adresse virtuelle", parAlex Peleg etUri Weiser d'Intel Corp., de brevet déposée le 30 Mars 1994, la poursuite d'une demande déposée en 1992, abandonné par la suite.

A magasins de cache de trace des instructions, soit après qu'ils ont été décodés, ou comme ils sont à la retraite. Généralement, les instructions sont ajoutées à tracer caches dans les groupes représentant soit individuels blocs de base ou des traces d'instructions dynamiques. Une trace dynamique («chemin de trace") ne contient que des instructions dont les résultats sont réellement utilisés, et élimine les instructions ci-dessous branches prises (car ils ne sont pas exécutées); une trace dynamique peut être une concaténation de plusieurs blocs de base. Ceci permet à l'unité d'extraction d'instruction d'un processeur pour aller chercher plusieurs blocs de base, sans avoir à vous soucier de branches dans le flux d'exécution.

Tracez des lignes sont stockés dans le cache de trace sur la base du compteur de programme de la première instruction dans la trace et un ensemble de prédictions de branchement. Cela permet de stocker différents chemins de trace qui commencent à la même adresse, chacun représentant différents résultats de la branche. Dans la recherche d'instructions étape d'un pipeline, le compteur de programme en cours avec un ensemble de prédictions de branchement est cochée dans le cache de trace d'un succès. Si il est un succès, une ligne de suivi est fourni pour aller chercher ce qui ne doit pas aller à un cache régulière ou à la mémoire de ces instructions. Le cache de trace continue d'alimenter l'unité d'extraction jusqu'à ce que la ligne de trace se termine ou jusqu'à ce que il ya une erreur de prédiction dans le pipeline. Si il ya un manque, une nouvelle trace commence à être construit.

Oligo caches sont également utilisés dans les processeurs tels queIntel Pentium 4 pour stocker des micro-opérations déjà décodés, ou des traductions d'instructions x86 complexes, de sorte que la prochaine fois qu'une instruction est nécessaire, il n'a pas à être décodé à nouveau.

Caches multi-niveaux

Un autre problème est le compromis fondamental entre la latence du cache et de taux de succès. Les plus gros caches ont un meilleur taux de succès mais plus la latence. Pour faire face à ce compromis, de nombreux ordinateurs utilisent plusieurs niveaux de cache, avec de petites caches rapides sauvegardés par les grandes caches plus lents.

Caches multi-niveaux fonctionnent généralement en cochant la plus petite de niveau 1 (L1) cache de premier; si elle frappe, le processeur passe à grande vitesse. Si le petit cache manque, la prochaine grande cache (L2) est cochée, et ainsi de suite, avant que la mémoire externe est cochée.

Comme la différence de latence entre la mémoire principale et le cache plus rapide est devenu plus grand, certains transformateurs ont commencé à utiliser autant que trois niveaux de cache sur puce. Par exemple, le Alpha 21164 (1995) avait 1 à 64 Mo L3 hors puce cache; IBM Power4 (2001) avait hors puce L3 caches de 32 Mo par processeur, partagées entre plusieurs processeurs; la Itanium 2 (2003) a eu un 6 Mo niveau unifié 3 (L3) cache sur puce; la Module Itanium 2 (2003) MX 2 intègre deux processeurs Itanium 2 avec un 64 Mo de cache L4 partagé sur un module de multi-puce qui était compatible broche à broche avec un processeur Madison; Intel Xeon MP produit le nom de code "Tulsa" (2006) dispose de 16 Mo de on-die cache L3 partagé entre deux c??urs de processeur; l'AMD Phenom II (2008) a jusqu'à 6 Mo sur-Dié cache L3 unifié; et le Intel Core i7 (2008) a un 8 Mo sur-die cache L3 unifié qui est inclusive, partagée par tous les c??urs. Les avantages d'un cache L3 dépendent des modèles d'accès de l'application.

Enfin, à l'autre extrémité de la hiérarchie mémoire, la CPU fichier de registres lui-même peut être considérée comme la plus petite, la plus rapide cache dans le système, avec la particularité qu'il est prévu dans le logiciel, typiquement par un compilateur, comme il alloue registres à tenir valeurs récupérées de la mémoire principale. (Voir notamment l'optimisation de la boucle nid.) Créer des fichiers parfois ont également hiérarchie: Le Cray-1 (circa 1976) avait 8 adresse "A" et 8 données scalaires de registres "S" qui étaient généralement utilisable. Il y avait aussi un ensemble de 64 adresses "B" et 64 données scalaires registres "T" qui ont eu plus de temps pour l'accès, mais étaient plus rapides que la mémoire principale. Les «B» et les registres "T" ont été fournis parce que le Cray-1 n'a pas eu un cache de données. (Le Cray-1 n'a, cependant, ont une mémoire cache d'instruction.)

Puces multi-core

Lors de l'examen d'une puce avec plusieurs c??urs, il ya une question de savoir si les caches doivent être partagés ou local pour chaque noyau. Mise en ??uvre de mémoire cache partagée introduit sans doute plus le câblage et la complexité. Mais alors, ayant une mémoire cache par puce , plutôt que de base , réduit considérablement la quantité d'espace nécessaire, et donc on peut inclure une plus grande mémoire cache. Typiquement, on trouve que le partage de cache L1 est indésirable car l'augmentation de latence est telle que chaque noyau se déroulera beaucoup plus lent que d'une puce single-core. Mais alors, pour le plus haut niveau (le dernier appelé avant d'accéder à la mémoire), ayant un cache global est souhaitable pour plusieurs raisons. Par exemple, une puce à huit c??urs avec trois niveaux peut inclure un cache L1 pour chaque core, d'un cache L3 partagé par tous les c??urs, avec le cache L2 intermédiaire, par exemple, un pour chaque paire de noyaux.

Séparée par rapport unifié

Dans une structure de cache séparé, instructions et de données sont mises en cache séparément, ce qui signifie que une ligne de cache est utilisé pour mettre en cache soit des instructions ou des données, mais pas les deux. Dans un un unifiée, cette contrainte est supprimée.

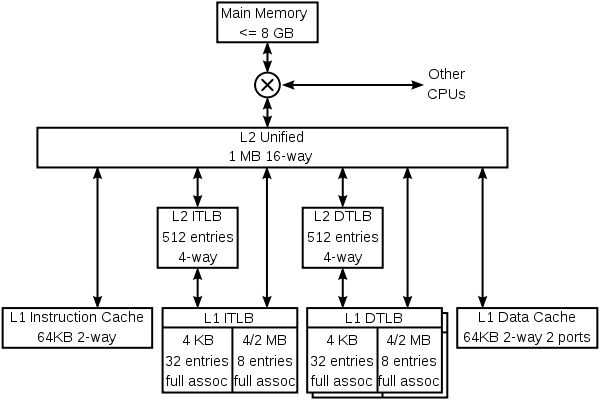

Pour illustrer à la fois la spécialisation et la mise en cache à plusieurs niveaux, voici la hiérarchie de cache du noyau K8 dans le AMDAthlon 64 CPU.

Le K8 dispose de 4 caches spécialisés: une cache d'instruction, une instruction TLB, une donnée TLB, et un cache de données. Chacun de ces caches est spécialisée:

- Le cache d'instruction conserve des copies des lignes de 64 octets de mémoire, et récupère 16 octets chaque cycle. Chaque octet dans ce cache est stocké dans dix bits plutôt que 8, avec les bits supplémentaires qui marquent les limites des instructions (ceci est un exemple de prédécodage). Le cache ne dispose que d' une protection de la parité plutôt que ECC parce que la parité est plus petit et toutes les données endommagées peut être remplacé par de nouvelles données lues à partir de la mémoire (qui a toujours une copie mise à jour d'instructions).

- L'instruction TLB conserve des copies des entrées de table de pages (PTE). L'instruction de chaque cycle d'extraction a son adresse virtuelle traduit par ce TLB en une adresse physique. Chaque entrée est de 4 ou 8 octets en mémoire. Parce que le K8 a une taille variable de la page, chacun des TLB est divisé en deux sections, l'une pour garder PTE qui correspondent pages de 4 Ko, et l'un de garder PTE que la carte 4 Mo ou 2 Mo de pages. La scission permet le circuit de correspondance entièrement associative dans chaque section d'être plus simple. Le système d'exploitation maps différentes sections de l'espace d'adressage virtuel avec différentes PTE de taille.

- Les données TLB possède deux copies qui gardent les entrées identiques. Les deux exemplaires permettent de deux données accède par cycle pour traduire les adresses virtuelles en adresses physiques. Comme l'instruction TLB, ce TLB est divisé en deux types d'entrées.

- Le cache de données conserve des copies des lignes de 64 octets de mémoire. Il est divisé en 8 banques (chacun stocker 8 Ko de données), et peut aller chercher deux données de 8 octets chaque cycle tant que ces données sont dans différentes banques. Il ya deux copies des étiquettes, parce que chaque ligne de 64 octets est réparti entre tous les 8 banques. Chaque copie d'étiquette gère l'un des deux accès par cycle.

Le K8 a aussi des caches de niveau multiple. Il ya instructions et de données TLB de second niveau, qui stockent seulement PTE cartographie 4 ko. Les deux instructions et de données caches, et les divers TLB, peuvent remplir de la grande unifié cache L2. Ce cache est exclusif à la fois l'instruction de caches L1 et de données, ce qui signifie que toute ligne de 8 octets ne peut être dans l'un des cache L1 d'instruction, le cache de données L1, ou le cache L2. Il est, toutefois, possible pour une ligne dans le cache de données pour avoir une PTE qui est aussi dans l'un des-le TLB système d'exploitation est chargé de tenir les TLBs cohérentes par rinçage des portions de ceux où les tables de pages en mémoire sont mis à jour.

Le K8 met également en cache des informations qui ne sont jamais stockées dans la mémoire d'informations de prédiction. Ces caches ne sont pas représentés dans le schéma ci-dessus. Comme il est habituel pour cette classe de CPU, le K8 a assez complexe prédiction de branchement, avec des tables qui aident à prévoir si les succursales sont prises et d'autres tables qui prédisent les objectifs de branches et de sauts. Certaines de ces informations est associé à des instructions, à la fois dans la mémoire cache de niveau 1 d'instruction et le cache secondaire unifié.

Le K8 utilise un truc intéressant pour stocker des informations de prédiction avec des instructions dans le cache secondaire. Lignes dans le cache secondaire sont protégés contre la corruption accidentelle de données (par exemple, par une grève de la particule alpha) soit par ECC ou la parité, selon que ces lignes ont été expulsés de données ou des caches de l'instruction primaire. Puisque le code de parité prend moins de bits que le code ECC, les lignes de la mémoire cache d'instruction ont quelques bits de rechange. Ces bits sont utilisés pour mettre en cache l'information de prédiction de branche associée à ces instructions. Le résultat net est que le prédicteur de branchement a une plus grande table de l'histoire effective, et a donc une meilleure précision.

Plus de hiérarchies

Autres processeurs ont d'autres types de prédicteurs (par exemple, la dérivation prédicteur magasin à charge dans le D??cembre Alpha 21264), et divers prédicteurs spécialisés sont susceptibles de prospérer dans les futurs processeurs.

Ces prédicteurs sont caches en ce qu'ils stockent des informations qui est coûteux à calculer. Une partie de la terminologie utilisée lors de l'examen des prédicteurs est la même que celle pour les caches (on parle d'un coup dans un prédicteur de branchement), mais ne sont pas prédictifs généralement considéré comme faisant partie de la hiérarchie de cache.

Le K8 garde les instructions et de données caches cohérentes dans le matériel, ce qui signifie que dans un magasin une instruction en suivant de près l'instruction de stockage va changer qu'à la suite de l'instruction. D'autres processeurs, comme ceux de la famille Alpha et MIPS, se sont appuyés sur le logiciel de garder le cache d'instruction cohérente. Magasins ne sont pas garantis à apparaître dans le courant de l'instruction jusqu'à ce qu'un programme appelle une installation de système d'exploitation pour assurer la cohérence.

Ex??cution

Cache lit sont le fonctionnement du processeur le plus commun qui prend plus d'un seul cycle. le temps d'exécution du programme a tendance à être très sensibles à la latence d'un cache de données hit niveau 1. Une grande partie de l'effort de conception, et de la puissance et de silicium souvent domaine sont dépensés rend les caches aussi vite que possible.

Le cache plus simple est un cache en correspondance directe pratiquement indexées. L'adresse virtuelle est calculée avec une vipère, la partie pertinente de l'adresse extraite et utilisée pour indexer une SRAM, qui renvoie les données chargées. L'octet de données est aligné dans un dispositif de décalage d'octet, et à partir de là est court-circuité à l'opération suivante. Il n'y a pas besoin de toute étiquette de vérifier dans la boucle intérieure - en fait, les balises ne devraient même pas être lus. Plus tard dans le pipeline, mais avant l'instruction de chargement est à la retraite, la balise pour les données chargées doit être lu et vérifié par rapport à l'adresse virtuelle pour vous assurer qu'il a été un succès de cache. Sur une miss, le cache est mis à jour avec la ligne de cache demandé et le pipeline est redémarré.

Un cache associatif est plus compliqué, car une certaine forme de balise doit être lue afin de déterminer quelle entrée de la mémoire cache pour sélectionner. Une N-way set-associative niveau 1 cache lit habituellement tous les N possibles balises et N données en parallèle, puis choisit les données associées à l'étiquette correspondante. caches de niveau-2 sauvent parfois la puissance en lisant les étiquettes d'abord, de sorte que un seul élément de données est lu à partir de la SRAM de données.

Le schéma de droite est destinée à clarifier la façon dont les divers champs de l'adresse sont utilisés. Le bit d'adresse 31 est le plus significatif, le bit 0 est le moins significatif. Le diagramme montre la SRAM, d'indexation et de multiplexage pour un 4 kB, 2-way set-associative, quasiment indexés et cache pratiquement balisé avec 64 lignes B, un 32b lire largeur et 32b adresse virtuelle.

Parce que le cache est de 4 ko et dispose de 64 lignes B, il n'y a que 64 lignes dans le cache, et nous lisons deux à la fois à partir d'une mémoire SRAM de Tag qui a 32 rangées, chacun avec une paire de 21 balises bits. Bien que toute fonction d'adresse virtuelle bits 31 à 6 pourrait être utilisé pour indexer le tag et SRAM de données, il est plus simple d'utiliser les bits les moins significatifs.

De même, parce que le cache est de 4 ko et dispose d'un chemin de lecture de 4 B, et lit deux manières pour chaque accès, la SRAM de données est de 512 lignes par 8 octets de large.

Un cache plus moderne pourrait être 16 ko, 4-way set-associative, pratiquement indexée, pratiquement laissé entendre, et physiquement marqué, avec 32 lignes B, 32b lire des adresses physiques largeur et 36b. La récurrence de chemin lire pour un tel cache est très similaire à la trajectoire ci-dessus. Au lieu de balises, vhints sont lues et comparées avec un sous-ensemble de l'adresse virtuelle. Plus tard dans le pipeline, l'adresse virtuelle est traduite en une adresse physique par le TLB, et l'étiquette physique est lu (une seule, comme les fournitures de vhint quel côté de la mémoire cache à lire). Enfin l'adresse physique est comparée à l'étiquette physique pour déterminer si un coup a eu lieu.

Certains modèles SPARC ont amélioré la vitesse de leurs caches L1 par quelques portes retards par l'effondrement de l'adresse additionneur virtuelle dans les décodeurs de SRAM. Voir Somme adressée décodeur.

Histoire

L'histoire des débuts de la technologie de cache est étroitement liée à l'invention et l'utilisation de la mémoire virtuelle. En raison de la rareté et le coût des semi-conducteurs mémoires, ordinateurs centraux début dans les années 1960 ont utilisé une hiérarchie complexe de la mémoire physique, mappé sur un espace de mémoire virtuelle plat utilisé par les programmes. Les technologies de mémoire seraient couvrir des semi-conducteurs, noyau magnétique, le tambour et disque. La mémoire virtuelle vu et utilisé par des programmes serait plat et la mise en cache serait utilisée pour récupérer les données et les instructions dans la mémoire plus rapide devant l'accès du processeur. Des études approfondies ont été effectuées pour optimiser les tailles de cache. Les valeurs optimales ont été trouvés à dépendre grandement sur ??????le langage de programmation utilisé avec Algol besoin le plus petit et Fortran et Cobol besoin des plus grandes tailles de cache.

Dans les premiers jours de la technologie de micro-ordinateur, un accès mémoire était seulement légèrement plus lent que l'accès inscrire. Mais depuis les années 1980 l'écart de performance entre le processeur et la mémoire a été de plus en plus. Microprocesseurs ont progressé beaucoup plus vite que la mémoire, en particulier en termes de fonctionnement fréquence, de sorte que la mémoire est devenue une performance goulot d'étranglement. Alors qu'il était techniquement possible d'avoir toute la mémoire principale aussi rapide que le CPU, un chemin plus économiquement viable a été prise: utiliser beaucoup de mémoire à basse vitesse, mais aussi introduire une petite mémoire cache haute vitesse pour atténuer l'écart de performance. Cela a fourni un ordre de grandeur plus capacités pour le même prix avec seulement une performance combinée légèrement réduite.

Premières implémentations TLB

Les premières utilisations documentés d'un TLB étaient sur ??????leGE645 et l'IBM 360/67, qui tous deux une mémoire associative utilisé comme un TLB.

Première cache de données

La première utilisation documentée d'un cache de données était sur ??????leIBMModel 85 System / 360.

Dans microprocesseurs x86

Comme le microprocesseurs x86 atteint des taux de 20 MHz d'horloge et au-dessus de la 386, de petites quantités de mémoire cache rapide ont commencé à être présenté dans les systèmes pour améliorer les performances. Ce fut parce que la DRAM utilisée pour la mémoire principale avait une latence importante, jusqu'à 120 ns, ainsi que des cycles de rafraîchissement. La cache a été construit à partir de plus cher, mais nettement plus rapide, SRAM, qui à l'époque avait latences environ 10 ns. Les premières caches étaient externe au processeur et généralement situé sur la carte mère sous la forme de huit ou neuf dispositifs DIP placés en prises pour permettre le cache en option ou la fonctionnalité de mise à niveau.

Certaines versions du processeur Intel 386 pourraient appuyer de 16 à 64Ko de cache externe.

Avec le Processeur 486, une mémoire cache de 8 kB a été intégré directement dans la filière de la CPU. Cette cache a été appelé Niveau 1 ou cache L1 pour la différencier de la plus lente sur la carte mère, ou de niveau 2 (L2). Ces caches-mère étaient beaucoup plus grandes, avec la taille la plus courante étant 256 kB. La popularité de cache sur la carte mère a continué à travers l' ère Pentium MMX, mais a été rendue obsolète par l'introduction de SDRAM et la disparité croissante entre les taux d'horloge de bus et des fréquences d'horloge du processeur, ce qui a provoqué cache sur la carte mère pour être seulement légèrement plus rapide que la mémoire principale .

Le prochain développement dans la mise en ??uvre de cache dans les microprocesseurs x86 a commencé avec lePentium Pro, qui a porté le cache secondaire sur le même package que le microprocesseur, cadencé à la même fréquence que le microprocesseur.

Sur la carte mère caches joui d'une popularité prolongées grâce aux AMD K6-2 et processeurs AMD K6-III qui utilisaient encore le vénérable Socket 7, qui a été précédemment utilisé par Intel avec des caches sur la carte mère. K6-III inclus 256 kb sur-die cache L2 et a profité de la cache à bord comme un cache de troisième niveau, nommé L3 (cartes mères avec un maximum de 2 Mo de cache à bord ont été produites). Après le Socket-7 est devenu obsolète, cache sur la carte mère a disparu des systèmes x86.

Le cache à trois niveaux a été utilisé à nouveau avec le premier introduction de plusieurs noyaux de processeur, où la L3 a été ajouté à la matrice de l'unité centrale. Il est devenu courant d'avoir les trois niveaux soient plus grande taille que la prochaine et, aujourd'hui, il est pas rare de trouver de niveau 3 tailles de cache de huit mégaoctets. Cette tendance semble se poursuivre dans un avenir prévisible.

La recherche actuelle

Design cache début concentre entièrement sur ??????le coût direct de cache et la RAM et la vitesse d'exécution moyenne. Plus de conceptions de cache récentes considèrent également l'efficacité énergétique, la tolérance de panne, et d'autres objectifs.

Il existe plusieurs outils disponibles pour les architectes informatiques pour aider à explorer les compromis entre le cycle de cache temps, d'énergie, et de la zone. Ces outils comprennent l'open-source simulateur de mémoire cache de cactus et l'open-source instruction SimpleScalar ensemble simulateur.

Cache multi-accès

Un cache multi-accès est un cache qui peut servir plus d'une demande à la fois. En accédant à un cache traditionnelle, nous utilisons normalement une adresse mémoire unique, alors que dans un cache multi-accès, nous pouvons demander N adresses à la fois - où N est le nombre de ports reliés par le processeur et la mémoire cache. L'avantage de ceci est que un processeur en pipeline peut accéder à la mémoire à partir de différentes phases de son pipeline. Un autre avantage est qu'il permet le concept de processeurs super-scalaires à travers les niveaux de cache différentes.